# Dual Priority Scheduling algorithm used in the nMPRA Microcontrollers

Subtitle as needed (paper subtitle)

#### Lucian Andries

Faculty of Electrical Engineering and Computer Science Stefan cel Mare University of Suceava Suceava, Romania andries.lucian2002ro@gmail.com

Abstract- In most of the safety-critical areas, including systems, avionics, automotive, and factory automation, the use of real-time time-trigger schedulers are encouraged due to their characteristics that does not allow interference to take place between safety-critical and non-critical components. Depending on the field where these types of schedulers are used, they can be categorized as preemptive or non-preemptive. In the automotive field, the non-preemptive schedulers are used where the system is safety relevant. The adoption of this strategy is used because offers a high predictability to the system, but can lead the system into failure. For this purpose it will be presented a solution where the switching of the context does not exist, therefore the use of critical sections is not needed any more. To achieve this performance we modified a static scheduler in a dynamic scheduler depending on the system status using Dual Priority scheduling and integrate the algorithm on a nMPRA processor. The new architecture provides a switching and response time for events within 5 to 8 machine cycles and guaranties that no task will suffer from starvation.

Keywords— dual priority scheduling, real time system, nMPRA microcontroller

### I. INTRODUCTION

Currently, the properties of a real time system depend, largely, on the scheduling algorithms used for the real time environment. The qualities of real-time scheduling algorithms have direct impact on the processing capacity of the system (number of tasks per unit time) and response time [1][2]. Using the fixed priority preemptive scheduling assure some benefits as a low runt-time overhead and the ability to support tight deadlines for high priority tasks [3]. The preemptive schedulers do not dominate non-preemptive schedulers in term of runtime overheads and amount of RAM memory consumption. In [3] the authors integrates both preemptive and non-preemptive schedulers which use the notion of preemption threshold [4], which was introduced by Express Analogic, Inc. to avoid unnecessary preemption. This new model, results in a dual priority system in which each task has a regular priority and a preemption thresholds which improves the schedulability of the tasks.

#### Gheorghita Gaitan

Faculty of Electrical Engineering and Computer Science Stefan cel Mare University of Suceava Suceava, Romania gaitan@eed.usv.ro

In [5] the proposed scheduling algorithm is Multiprocessor Dual Priority (MPDP), which splits priorities into three bands, upper, middle and lower. The hard task, that are considered period tasks, are assign two priorities, one for upper and one for lower band. The aperiodic tasks are considered as soft tasks and are assigned the priority of the middle band, which may be preempted by other hard tasks with higher priorities in the same band, by aperiodic tasks in the middle band or by any periodic task in the upper priority band. In this approach is guaranteed that the aperiodic tasks will have a reasonable answer in time, while the utilization of the system, is enhance.

The proposed model looks similar with our approach, with some differences:

- Our proposed Scheduler uses two different algorithms to schedule the tasks in order to have a functioning system no matter how is the load of the tasks from the system.

- The scheduler uses three different priority tasks to use two different scheduling algorithms.

#### II. THE NMPRA ARHITECTURE

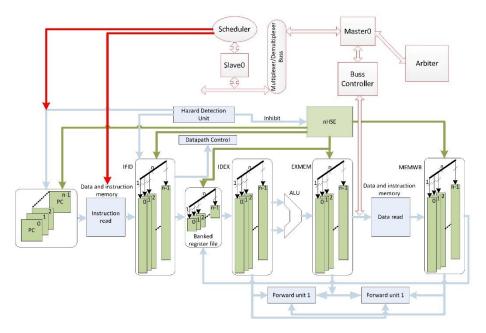

The first version of nMPRA has been defined in [6] and [7]. In [8] the nMPRA architecture has been improved for the scheduling process. To the current nMPRA architecture was added a slow bus with a Buss Controller and a peripheral in which the scheduling algorithm was embedded (Fig. 1). The scheduling algorithm was removed from the nHSE block and embedded into a peripheral because the hardware tasks will be configured with the help of its internal registers. At this moment the processor architecture have been transformed into microcontroller architecture.

This new approach optimizes the switching of the hardware tasks in terms of silicon costs and system complexity. During this process we encounter some synchronization issue, caused by the current architecture of the processor, MIPS with 5 pipeline stages. In order to stop a working task the Program Counter (PC) must be stopped. The switch process of a task is really simple and is done in two steps.

Fig. 1. The nMPRA architecture (source [8])

- Stop the PC of current task.

- · Select the appropriate task to share the resources.

From this description we can think that the switching of a task can be done in 1 machine cycle, because the stopping of the PC and the selection of the appropriate input/output of the multiplexer/demultiplexer can be done simultaneously.

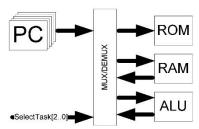

It could be true if there were no decencies with the RAM and ALU that are shared. So when the <code>SelectTask[2.0]</code> bus (Fig. 2) will have a different value, in order to select the new task, the ROM, ALU and ALU will no longer be available for the current task.

Fig. 2. Simplified nMPRA architecture

We've choose to wait 3 machine cycles to solve the synchronization issue. The other 2 machine cycles are used to synchronize the next task program counter address with the ROM memory and the instruction fetch pipeline register

because the Scheduler and the program counter are using 3 quadrature clock signals.

# III. THE PROPOSED DUAL PRIORITY ALGORITHM

In this paper we are treating the dynamic scheduling. In the [9] the switching time was between 1 and 3 machine cycles while in this paper the overall switching time of a task is 5 machine cycles because the RAM, ALU and ROM are shared between multiple resources (Fig. 2) using only one big multiplexer/demultiplexer. In order to have a better understanding of the algorithm we are going to reuse and detail some of the information from [9].

In the following lines, the classes that each task can belong are presented:

- The class of active tasks, which has the higher priority (the tasks will be inserted only in the active task queue (ATQ)): will schedule the tasks, based on priorities, only in the Running State (RS) of the Scheduler.

- The class of interrupted tasks, which has the second priority (the tasks will be inserted only in the interrupted task queue (ITQ)): will schedule the tasks, based on priorities, only in the Idle State (IS) of the Scheduler.

- The long execution tasks class (significantly exceed the base period T corresponding to the priority task), which as the least priorities (the tasks will be inserted

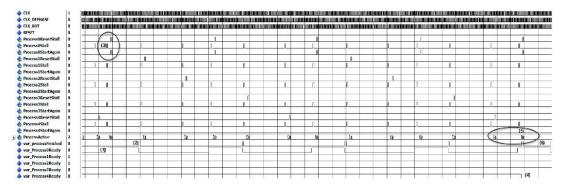

Fig. 3. Overall view of the task switching system

only in the long task queue (LTQ)): will schedule the tasks, based on ROUND ROBIN (RR) algorithm, only in the Idle State (IS) of the Scheduler.

Emerged into the Scheduler, a global Round Robin timer (TRB) exists that is used to supervise the active time of the current task and also used as a task occurrence for the long tasks

Knowing that the timer is used to measure the active time of a task and stop it if it takes too long to execute, we will have to be careful with the time values that are going to be used for the tasks supervision. In order to have a functional scheduler, the TRB should be initialize with the occurrence of the slowest task from the system or less. However, this configuration depends on the system architect.

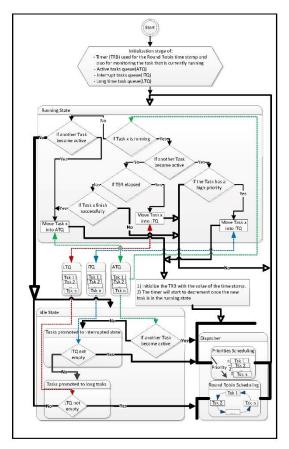

In Fig. 4 is presented the operational flowchart of the Scheduler (event driven), which is driven by the main clock signal of the processor. The events can be generated by the expiration of the TRB and the activation of the tasks.

In order to illustrate the algorithm better we are going to assume that processor executes 5 tasks with 5 different priorities.

At some point one task became active, the TRB will start to decrement and the Scheduler will enter the RS. If the task, for some reason, takes more time than usual, the TRB will expire and the current task will be inserted into the long task queue. But if the task is going to finish its execution before TRB expires, the Scheduler will enter IS.

Assume that another task became active, starts to execute code and another task, with greater priority, became active. The first task will be interrupted and inserted into the ITQ and the task with greater priority will take its place. After active task finish its execution, the Scheduler will leave the RS and enter IS and the interrupted task will resume its execution. For a better illustration of this example we assume that all the 5 tasks became active, in the end one task will run and the other 4 will be inserted into the ITQ. After the current task finish its execution and the Scheduler leave RS and enter IS the 4 task will be scheduled based on priority.

Now let's take another example. All of the tasks are slow and will be inserted into the LTQ. After the Scheduler will leave RS and enter IS, the priorities of the current tasks will not matter, because the long tasks will be scheduled based on RR algorithm. The amount of time that each task will have is equal with the time from TRB. When a task finishes its execution, during this state, it will be inserted into the ATQ and removed from LTQ.

Because of this TRB and the RR algorithm the system cannot be blocked by any task.

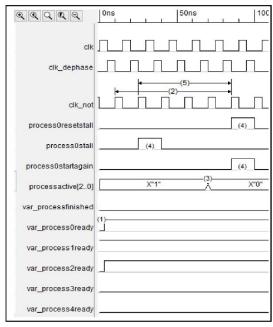

In Fig. 3 are presented 5 tasks that are scheduled by the algorithm. In the following lines there will be a description regarding the relevant signals, from the point of view, that are used in switching process:

a) clk, clk\_dephase,clk\_not – are the clock signals for different modules from microcontroller.

b) processXstall (X will have values from 0 to 4): force the current task to enter low power mode. In this state the task will not execute any instructions.

c) processXresetstall (X will have values from 0 to 4): wake up the current task that is in low power consumption.

d) processXstartagain (X will have values from 0 to 4): select the active address, with the help of the program counter, of the task that is going to be released.

e) Processactive[2:0]: represents the number of the active task.

f) var\_processXready (X will have values from 0 to 4): represents the event when a task became active. That does not mean that it will start to run. The signal will be high as long as the task is executing code or is active and in low power mode or just interrupted.

g) var\_processfinished: task finishes execution.

In Fig. 3 can be seen that the Task0, which has the highest priority, is scheduled periodically ((1) from Fig. 3). The var\_process0ready signal will be high as long as the task is executing code. The var\_processfinished signal ((2) from Fig. 3) shows that the Task0 finish its execution successfully and enter low power mode ((3) from Fig. 3).

Fig. 4. The flowchart of a scheduler with a dual priority algorithm proposed (Figure 3 from [9]).

In (5) from Fig. 3 a task switch take place. Task4 finish its execution successfully ((4) and (6) from Fig. 3) and Task0 will start to execute code.

If the TRB and the occurrence of the tasks are not chosen properly, the following situation can occur:

- Priority inversion: There are 3 tasks with different priorities. The task, with intermediary priority, is running and is interrupted by the second task with higher priority. The task that was interrupted is now in the ITQ and the current task finishes its execution, but at the same time, the third task, with lower priority became active. In this particularly case the task from ITQ will not run, even though it has higher priority, because the new task is located into the ATQ

- Task starvation: Assume that we have 10 tasks with different and same priorities. If one task is interrupted by another task, with higher priority, this task will be

introduced into the ITQ. From this point forward all of the tasks are going to succeed properly forcing the Scheduler to remain in the RS. Because the ITQ and LTQ are used only in the IS, this task will starve. If another task is interrupted, it will be inserted into the ITQ. At this moment the balanced is broken because the Scheduler will have time to enter the IS and one of the two task will be inserted again into the ATQ based on priority.

The particularly cases that were mention above can be avoided by choosing the right occurrence for each task in order to let the Scheduler enter IS. Let's assume that we enter in one of the particularly cases described abode because the frequency chosen for the processor is too small for the complexity of the whole system. The situation can occur quite easily because the project manager did not foresee that the functionality of the entire project can be increased considerably at the demand of the customer.

In this case the system can be configured to work only in a Round Robin manner, each task will have the same occurrence. The configuration of the whole system will not be affected at all by this approach because the only thing the programmer has to do is to insert the code from each task into an infinite loop. Because of this infinite loop the task will never end and each task will be promoted to LTQ.

#### IV. RESULTS

The first steps, which were taken to obtain the current microcontroller architecture was an approach from simple to complex.

The first and the most important step was the designing of a simple, but functional MIPS processor. After a proper testing, the processor architecture was improved with more than 35 instructions, ultimately leading to a number of 42 instructions. The next steps, that were more complex, were to modify the current processor architecture to support 5 hardware threads. In order to achieve these results the following resources were added:

- a) A big multiplexer/demultiplexer: used to select the active task.

- $b) \ A \ slow \ bus:$  that is clocked at the microcontroller clock line.

- c) The dual priority scheduler: used to switch tasks.

The whole architecture was design using VHDL hardware description language (VHDL 93). Altium Designer 2014 was used, only as a text editor, to include the individual VHDL module and create the architecture. The design created was simulated using ModelSim Altera Started Edition 10.1d. The only stimulus applied to the microcontroller was the 3 quadrature clock signals because the ROM memory was already initialized with the machine code for all 5 tasks.

The following results were observed, in normal operation, at key points. In the following lines we are going to detail the steps required to do a task switch:

a) var\_process0ready ((1) from Fig. 5)) signal represents the event occurring after activation of the first task. Because no jump instruction is performed all of the active task will be stopped with the help of processXstall (X will have values from 0 to 4) signal. The process1ready will remain active as a sign that the task is still active. At this moment task1 will be in the ITQ.

- b) Wait one clock cycle.

- c) Processactiv signal selects thread 0 as the active one (3) from Fig. 5).

- *d)* Process0resetstall and process0startagain signals are activated ((4) from Fig. 5).

As we can see from Fig. 5 the response time of the scheduler is one machine cycle (between (2) and (5)), the time spent after the task with higher priority became active and the starting of executing code (between (2) and (5) from Fig. 5) is done in 5 machine cycles in an interval of 75ns, where the period of the clock is 15 ns.

#### V. CONCLUSIONS

The current paper presented, in a more detailed manner, the dynamic dual priority algorithm presented briefly in the [9]. The main idea of the dual priority algorithm was to keep a functional operating system no matter how difficult were the requirements of the system.

Fig. 5. Time for a task switch

The algorithm, shown in the Fig. 3, will ensures the execution of each task, even for those states that are different from normal state, only if the occurrence of the tasks and the time for the TRB is chosen properly.

If these two requirements are not met, the scheduler will not work properly because one of the two unfortunate situations, explained above, will happen. This situation is not a consequence of the scheduling algorithm being implemented in hardware, the same situation could happened to a scheduling algorithm implemented in software. The conclusion from [9] persist in this paper, even though exists the situation explained above. The nMPRA microcontroller provides very good switching times, constant 5 machine cycles. Because the switch of the context and the critical sections are missing the current architecture is more robust and less susceptible to invalid data due to operating system context switch.

### Acknowledgment

This paper was supported by the project "Sustainable performance in doctoral and post-doctoral research PERFORM - Contract no. POSDRU/159/1.5/S/138963", project co-funded from European Social Fund through Sectorial Operational Program Human Resources 2007-2013.

### References

- N.C. Gaitan, "Real-time Acquisition of the Distributed Data by using an Intelligent System", Electronics and Electrical Engineering JOURNAL, Kaunas University (Lithuania) No. 8 (104), pp. 13-18, ISSN 1392-1215, October 2010.

- [2] C. Liu, 1. Layland, "Scheduling algorithms for multiprogramming in real-time environment," Journal of ACM, 1973,20(1), pp.46-61.

- [3] Yun Wang and Manas Saksena "Scheduling Fixed-Priority Tasks with Preemption Threshold", RTCSA'99, Hongkong, December 1999.

- [4] William Lamie. Preemption-threshold. White Paper, Express Logic Inc. Available at http://rtos.com/products/threadx/.

- [5] J. M. Ban'us, A. Arenas and J. Labarta, "Dual priority algorithm to schedule real-time tasks in a shared memory multiprocessor", International Parallel and Distributed Processing Symposium, 2003.

- [6] E. Dodiu, V.G. Gaitan, A. Graur, "Custom designed CPU architecture based on a hardware scheduler and independent pipeline registers – architecture description", IEEE 35'th Jubilee International Convention on Information and Communication Technology, Electronics and Microelectronics, Croatia, May 2012.

- [7] E. Dodiu and V.G. Gaitan, "Custom designed CPU architecture based on a hardware scheduler and independent pipeline registers – concept and theory of operation", 2012 IEEE EIT International Conference on Electro-Information Technology, Indianapolis, IN, USA, 6-8 May 2012, ISBN: 978-1-4673-0818-2, ISSN: 2154-0373.

- [8] V.G. Gaitan, N.C. Gaitan, I. Ungurean, "CPU Arhitecture based on a Hardware Scheduler and Independent Pipeline Registers", in review, IEEE Transactions on VLSI System, 2014.

- 9] N. Gaitan and A. Lucian, "Using Dual Priority Scheduling to Improve the Resource Utilization in the nMPRA Microcontrollers", IEEE 12th International Conference on DEVELOPMENT AND APPLICATION SYSTEMS, Succava, Romania, May 15-17, 2014.

# Proceedings of 2014 18<sup>th</sup> International Conference on System Theory, Control and Computing (ICSTCC)

(Joint conference SINTES 18, SACCS 14, SIMSIS 18)

October 17 - 19, 2014

Editors: Mihaela Hanako Matcovschi Lavinia Ferariu Florin Leon

Technical Co-sponsor:

Institute of Electrical and Electronics Engineers - Control Systems Society

Co-organizers:

Gheorghe Asachi Technical University of Iasi Faculty of Automatic Control and Computer Engineering

Copyright and Reprint Permission: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. For reprint or republication permission, email to IEEE Copyrights Manager at pubs-permissions gieee.org.

All rights reserved. Copyright ©2014 by IEEE.

ISBN 978-1-4799-4602-0

# 18th International Conference on System Theory, Control and Computing

October 17-19, 2014, Sinaia, Romania

Program at a Glance Friday Saturday Sunday Author Index Keyword Index

### Program at a Glance

ICSTCC 2014 Technical Program Friday October 17, 2014 Friday Saturday Sunday

| ICSTCC 2014 Technical Program Friday October 17, 2014 |                                                                      |                                       |                      |                      |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|--|--|

| Track T1                                              | Track T2                                                             | Track T3                              | Track T4             | Track T5             |  |  |

|                                                       |                                                                      | 09:00-09:20                           |                      |                      |  |  |

|                                                       |                                                                      | Miorita<br>Plenary Session FrPOC      |                      |                      |  |  |

|                                                       | Pienary Session FIFOC                                                |                                       |                      |                      |  |  |

|                                                       | Opening Ceremony                                                     |                                       |                      |                      |  |  |

|                                                       | 09:20-10:05                                                          |                                       |                      |                      |  |  |

| Miorita                                               |                                                                      |                                       |                      |                      |  |  |

| Plenary Session FrPP1                                 |                                                                      |                                       |                      |                      |  |  |

|                                                       | Perspectives on Software Integration for Intelligent Robotic Systems |                                       |                      |                      |  |  |

| 10:05-10:50                                           |                                                                      |                                       |                      |                      |  |  |

| Miorita                                               |                                                                      |                                       |                      |                      |  |  |

|                                                       | Plenary Session FrPP2                                                |                                       |                      |                      |  |  |

|                                                       | <u>Visual Data U</u>                                                 | nderstanding and UI Control with Huma | ns in the Loop       |                      |  |  |

|                                                       |                                                                      |                                       |                      |                      |  |  |

| 11:10-12:50                                           | 11:10-12:50                                                          | 11:10-12:50                           | 11:10-12:50          | 11:10-12:50          |  |  |

| Miorita                                               | Ara                                                                  | Carpati                               | Laca                 | Bucegi 1             |  |  |

| Regular Session FrA1                                  | Regular Session FrA2                                                 | Invited Session FrA3                  | Regular Session FrA4 | Regular Session FrA5 |  |  |

| Linear Systems                                        | Hardware Design                                                      | Fractional Order Modeling and Control | <u>Optimisation</u>  | Software Engineering |  |  |

|                                                       | -                                                                    |                                       | ·                    |                      |  |  |

|                                                       |                                                                      | 15:00-15:50                           |                      |                      |  |  |

|                                                       |                                                                      | Miorita                               |                      |                      |  |  |

| Plenary Session FrPP3                                 |                                                                      |                                       |                      |                      |  |  |

| How to Cluster Data: Algorithms and Validation        |                                                                      |                                       |                      |                      |  |  |

| ·                                                     |                                                                      |                                       |                      |                      |  |  |

| 16:10-18:10                                           | 16:10-18:10                                                          | 16:10-18:10                           | 16:10-18:10          | 16:10-18:10          |  |  |

| Miorita                                               | Ara                                                                  | Carpati                               | Laca                 | Bucegi 1             |  |  |

| Invited Session FrB1                                  | Invited Session FrB2                                                 | Regular Session FrB3                  | Regular Session FrB4 | Regular Session FrB5 |  |  |

| New Trends in Robotic Systems                         | Real Time Systems Applications                                       | Applied Informatics                   | Control Applications | Nonlinear Systems    |  |  |

ICSTCC 2014 Technical Program Saturday October 18, 2014 Friday Saturday Sunday Top

| ICSTCC 2014 Technical Program Saturday October 18, 2014                      |                             |                                                 |                                          |                                   |  |

|------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|------------------------------------------|-----------------------------------|--|

| Track T1                                                                     | Track T2                    | Track T3                                        | Track T4                                 | Track T5                          |  |

|                                                                              |                             | 09:00-09:45<br>Miorita<br>Plenary Session SaPP4 |                                          |                                   |  |

| Developing the Industrial Internet of Things with a Network Centric Approach |                             |                                                 |                                          |                                   |  |

|                                                                              |                             | 09:45-10:30<br>Miorita<br>Plenary Session SaPP5 |                                          |                                   |  |

| Intelligent Cyber - Energy Systems                                           |                             |                                                 |                                          |                                   |  |

| 10:50-12:50                                                                  | 10:50-12:50                 | 10:50-12:50                                     | 10:50-12:50                              | 10:50-12:50                       |  |

| Miorita                                                                      | 10.50-12.50<br>Ara          | Carpati                                         | Laca                                     | Bucegi 1                          |  |

| Invited Session SaC1                                                         | Regular Session SaC2        | Regular Session SaC3                            | Regular Session SaC4                     | Invited Session SaC5              |  |

| Bio-Inspired Dynamical Systems                                               | Predictive Control          | Robust Control                                  | Distributed Systems and Web Applications | Interactions in Complex Systems   |  |

|                                                                              |                             |                                                 |                                          |                                   |  |

| 15:00-16:40                                                                  | 15:00-16:40                 | 15:00-16:40                                     | 15:00-16:40                              | 15:00-16:40                       |  |

| Miorita<br>Invited Session SaD1                                              | Ara<br>Invited Session SaD2 | Carpati<br>Regular Session SaD3                 | Laca<br>Regular Session SaD4             | Bucegi 1<br>Regular Session SaD5  |  |

| Advances in Automotive Control - I                                           | Visual Computing - I        | Embedded Systems                                | Control System Design                    | Hybrid and Discrete Event Systems |  |

|                                                                              |                             |                                                 |                                          |                                   |  |

| 17:00-18:40                                                                  | 17:00-18:40                 | 17:00-18:40                                     | 17:00-18:40                              | 17:00-18:40                       |  |

| Miorita                                                                      | Ara                         | Carpati                                         | Laca                                     | Bucegi 1                          |  |

| Invited Session SaE1                                                         | Invited Session SaE2        | Regular Session SaE3                            | Regular Session SaE4                     | Regular Session SaE5              |  |

| Advances in Automotive Control - II                                          | Visual Computing - II       | Identification, Modelling and Simulation        | Theory of Algorithms                     | Agent-Based Systems               |  |

# ICSTCC 2014 Technical Program Sunday October 19, 2014 Friday Saturday Sunday Top

| ICSTCC 2014 Technical Program Sunday October 19, 2014 |                                            |                                                |                                             |                                                 |

|-------------------------------------------------------|--------------------------------------------|------------------------------------------------|---------------------------------------------|-------------------------------------------------|

| Track T1                                              | Track T2                                   | Track T3                                       | Track T4                                    | Track T5                                        |

| 10:00-12:00<br>Miorita<br>Regular Session SuF1        | 10:00-12:00<br>Ara<br>Regular Session SuF2 | 10:00-12:00<br>Carpati<br>Regular Session SuF3 | 10:00-12:00<br>Laca<br>Regular Session SuF4 | 10:00-12:00<br>Bucegi 1<br>Regular Session SuF5 |

| Networked Control                                     | Robot and Motion Control                   | Computational Intelligence                     | Signal Processing                           | Control Engineering                             |

12:30-13:00 Miorita Plenary Session SuPCC

Closing Ceremony

# 18th International Conference on System Theory, Control and Computing

October 17-19, 2014, Sinaia, Romania

Program at a Glance Friday Saturday Sunday Author Index Keyword Index

# Technical Program for Friday October 17, 2014

To show or hide the keywords and abstract of a paper (if available), click on the paper title

Open all abstracts

Close all abstracts

FrPOC Plenary Session, Miorita

Opening Ceremony

Chair: Voicu, Mihail Gheorghe Asachi Tech. Univ. of Iasi

Co-Chair: Rasvan, Vladimir Univ. of Craiova

FrPP1 Plenary Session, Miorita

Perspectives on Software Integration for Intelligent Robotic Systems

Cervera, Enric Jaume-I Univ. of Castello de la

Plan

Chair: Rasvan, Vladimir Univ. of Craiova

FrPP2 Plenary Session, Miorita

Visual Data Understanding and UI Control with Humans in the Loop

Charvillat, Vincent Univ. of Toulouse

Chair: <u>Lazar, Corneliu</u> Gheorghe Asachi Tech. Univ. of Iasi

FrPP3 Plenary Session, Miorita

How to Cluster Data: Algorithms and Validation

Fränti, Pasi Univ. of Eastern Finland

Chair: Minzu, Viorel Dunarea de Jos Univ. of Galati

FrA1 Regular Session, Miorita

Linear Systems

Chair: Oara, Cristian Pol. Univ. of Bucharest

Co-Chair: Pastravanu, Octavian-Cezar Gheorghe Asachi Tech. Univ. of Iasi

11:10-11:30, Paper FrA1.1

On a Conjecture in Stability Analysis of Polytopic Systems – Mimicking Spectral Radius Properties

from Real to Complex Matrices

<u>Pastravanu, Octavian-Cezar</u>

<u>Matcovschi, Mihaela-Hanako</u>

Gheorghe Asachi Tech. Univ. of Iasi

Gheorghe Asachi Tech. Univ. of Iasi

11:30-11:50, Paper FrA1.2

Study of the Interaction between a One Degree of Freedom Force Augmenting Device and a

Human Operator

Gadi, Suresh Kumar Pol. Univ. of Aquascalientes

Osorio-Cordero, Antonio Cinvestav

Lozano, Rogelio Univ. of Tech. of Compiègne

11:50-12:10, Paper FrA1.3

Minimal Factorization of Transfer Matrices for Generalized Systems

Flutur, Cristian Pol. Univ. of Bucharest

Oara, Cristian Pol. Univ. of Bucharest

12:10-12:30, Paper FrA1.4

Sufficient Conditions for Stabilisability of Decentralised LTI Systems: Weighted Directed Graph

<u>Approach</u>

Abdolmaleki, Mohammad Univ. of Melbourne

Aldeen, Mohammad Univ. of Melbourne

12:30-12:50, Paper FrA1.5

Outer Bound Estimations for the Spectral Radii of Interval Matrices

Matcovschi, Mihaela-HanakoGheorghe Asachi Tech. Univ. of IasiPastravanu, Octavian-CezarGheorghe Asachi Tech. Univ. of IasiVoicu, MihailGheorghe Asachi Tech. Univ. of Iasi

FrA2 Regular Session, Ara

Hardware Design

Chair: <u>Ungureanu, Florina</u>

Co-Chair: <u>Florea, Adrian</u>

Gheorghe Asachi Tech. Univ. of Iasi

Lucian Blaga Univ. of Sibiu

11:10-11:30, Paper FrA2.1

Enhancing the Sniper Simulator with Thermal Measurement

Florea, Adrian

Lucian Blaga Univ. of Sibiu

Buduleci, Claudiu-Raul

Lucian Blaga Univ. of Sibiu

Chiş, Radu

Tehnical Univ. of Cluj-Napoca

Gellert, Arpad

Lucian Blaga Univ. of Sibiu

Vintan, Lucian

Lucian Blaga Univ. of Sibiu

11:30-11:50, Paper FrA2.2

Offline Error-Detection Strategies for the IDEA NXT Crypto-Algorithm

Opritoiu, Flavius

Pol. Univ. of Timisoara

Bozesan, Andreea

Pol. Univ. of Timisoara

Vladutiu, Mircea

Pol. Univ. of Timisoara

11:50-12:10, Paper FrA2.3

Dual Priority Scheduling Algorithm Used in the Nmpra Microcontrollers

Andries, Lucian Stefan Cel Mare Univ. of Suceava

Gaitan, Vasile Gheorghita Stefan Cel Mare Univ. of Suceava

12:10-12:30, Paper FrA2.4

Sensorial System for HYPER-REDUNDANT ARM

Vladu, Ionel Cristian

Univ. of Craiova

Vladu, Ileana

Univ. of Craiova

Ivanescu, Mircea

Univ. of Craiova

Strîmbeanu, Daniel

Univ. of Craiova

# 12:30-12:50, Paper FrA2.5

Hardware Event Handling in the Hardware Real-Time Operating Systems

Moisuc (Ciobanu), Elena-EugeniaStefan Cel Mare Univ. of SuceavaLarionescu, Alexandru-BogdanStefan Cel Mare Univ. of SuceavaUngurean, IoanStefan Cel Mare Univ. of Suceava

#### FrA3 Invited Session, Carpati

### Fractional Order Modeling and Control

Chair: Copot, Cosmin Ghent Univ.

Co-Chair: Muresan, Cristina Ioana Tech. Univ. of Cluj Napoca

Organizer: Copot, Cosmin Ghent Univ.

Organizer: Muresan, Cristina Ioana Tech. Univ. of Cluj-Napoca

# 11:10-11:30, Paper FrA3.1

Stabilizing Control Strategies: A Comparison between the Fractional Order Controller and the IMC (I)

Folea, SilviuTech. Univ. of Cluj-NapocaMarton, BotondTech. Univ. of Cluj-NapocaMuresan, Cristina IoanaTech. Univ. of Cluj-Napoca

#### 11:30-11:50, Paper FrA3.2

Optimization of Fractional PID Controller by Maximization of the Criterion That Combines the Integral Gain and Closed-Loop System Bandwidth (I)

Jakovljevic, Boris

Univ. of Novi Sad

Rapaić, Milan

Univ. of Novi Sad

Šekara, Tomislav

Univ. of Belgrade

Jelicic, Zoran

Univ. of Novi Sad

# 11:50-12:10, Paper FrA3.3

Visual Servo Control of a Steward Platform Using Fractional-Order PID Controller (I)

Copot, Cosmin

Ghent Univ.

Ionescu, Clara

Ghent Univ.

De Keyser, Robin M.C.

Ghent Univ.

# 12:10-12:30, Paper FrA3.4

Fractional Order Control on a Wind Turbine Benchmark (I)

Viveiros, CarlaInst. Superior De Engenharia De LisboaMelicio, RuiUniv. De EvoraIgreja, José Manuel CardosoInst. Superior De Engenharia De LisboaMendes, VictorInst. Superior De Engenharia De Lisboa

### 12:30-12:50, Paper FrA3.5

Benign and Malignant Breast Tumors: Diagnosis Using Fractal Measures (I)

<u>Dobrescu, Radu</u> Pol. Univ. of Bucharest

Ichim, Loretta

Pol. Univ. of Bucharest

Mocanu, Stefan

Pol. Univ. of Bucharest

Popescu, Dan

Pol. Univ. of Bucharest

# FrA4 Regular Session, Laca

Optimisation

Chair: Shcherbakov, Pavel Moscow Inst. for Control Sciences, RAS

Co-Chair: Caruntu, Constantin - Florin Gheorghe Asachi Tech. Univ. of Iasi

### 11:10-11:30, Paper FrA4.1

Precedence Constraints Treatment in Ant Colony Optimization

Serbencu, Adrian EmanoilDunarea De Jos Univ. of GalatiMinzu, ViorelDunarea De Jos Univ. of GalatiSerbencu, AdrianaDunarea De Jos Univ. of Galati

### 11:30-11:50, Paper FrA4.2

On the Computation of Lyapunov Functions for Discrete-Time Nonlinear Systems

Bobiti, Ruxandra Valentina Eindhoven Univ. of Tech

Lazar, Mircea Eindhoven Univ. of Tech

# 11:50-12:10, Paper FrA4.3

Optimal Control with Fixed-End Point for Linear Perturbed Systems

Ostafi, Florin Gheorghe Asachi Tech. Univ. of Iasi

Botan, Corneliu Gheorghe Asachi Tech. Univ. of Iasi

### 12:10-12:30, Paper FrA4.4

Quadratic Image of a Ball: Towards Efficient Description of the Boundary

Polyak, Boris T. Moscow Inst. for Control Sciences

Shcherbakov, Pavel Moscow Inst. for Control Sciences

Khlebnikov, Mikhail Moscow Inst. for Control Sciences

# 12:30-12:50, Paper FrA4.5

Trajectory Planner for Mobile Robots Using Particle Swarm Optimization

<u>Solea, Razvan</u>

Dunarea De Jos Univ. of Galati

<u>Cernega, Daniela Cristina</u>

Dunarea De Jos Univ. of Galati

# FrA5 Regular Session, Bucegi 1

Software Engineering

Chair: <u>Iliescu, Dragos</u>

Co-Chair: <u>Costeniuc, George</u>

Univ. Pol. of Bucharest

Continental Automotive Romania SRL Iasi

# 11:10-11:30, Paper FrA5.1

Is FBDK Suitable for Developing and Implementing Process Control Optimization Problems?

Rohat, Oana Pol. Univ. of Bucharest Popescu, Dan Pol. Univ. of Bucharest

#### 11:30-11:50, Paper FrA5.2

Double Precision Stencil Computations on Kepler GPUs

Vizitiu, Anamaria

Transilvania Univ. of Brasov

Itu, Lucian

Lucian Blaga Univ. of Sibiu

Lazar, Laszlo

SC Siemens SRL

Suciu, Constantin

SC Siemens SRL

### 11:50-12:10, Paper FrA5.3

Assisted Management of Product Data - a PDM Application Proposal

Iliescu, Dragos

Pol. Univ. of Bucharest

Ciocan, Ion

Pol. Univ. of Bucharest

Mateias, Ion

Doosan IMGB Bucharest

### 12:10-12:30, Paper FrA5.4

Semantic Report Search Engine - Questor

Vasilateanu, AndreiPol. Univ. of BucharestGoga, NicolaePol. Univ. of BucharestMoldoveanu, AlinPol. Univ. of Bucharest

# 12:30-12:50, Paper FrA5.5

SaaS Solutions for Small-Medium Businesses Developer's Perspective on Creating New SaaS

**Products**

Resceanu, Ionut Cristian

Univ. of Craiova

Resceanu, Cristina Floriana

Univ. of Craiova

Simionescu, Sabin Mihai

SC White Pyramid SRL

#### FrB1 Invited Session, Miorita

### New Trends in Robotic Systems

Chair: Cervera, Enric

Co-Chair: Panescu, Doru-Adrian

Organizer: Cervera, Enric

Organizer: Borangiu, Theodor

Organizer: Panescu, Doru-Adrian

Organizer: Panescu, Doru-Adrian

Organizer: Panescu, Doru-Adrian

Organizer: Burlacu, Adrian

Organizer: Burlacu, Adrian

Jaume-I Univ. of Castello de la Plana

Pol. Univ. of Bucharest

Gheorghe Asachi Tech. Univ. of Iasi

Gheorghe Asachi Tech. Univ. of Iasi

### 16:10-16:30, Paper FrB1.1

Integration of Mobile Agents in Distributed Manufacturing Control (I)

Raileanu, Silviu

Pol. Univ. of Bucharest

Borangiu, Theodor

Pol. Univ. of Bucharest

Ivanescu, Nick Andrei

Pol. Univ. of Bucharest

Morariu, Octavian

Pol. Univ. of Bucharest

### 16:30-16:50, Paper FrB1.2

Trading Optimality for Computational Feasibility in a Sample Gathering Problem (I)

Kloetzer, Marius

Gheorghe Asachi Tech. Univ. of Iasi

Ostafi, Florin

Gheorghe Asachi Tech. Univ. of Iasi

Burlacu, Adrian

Gheorghe Asachi Tech. Univ. of Iasi

# 16:50-17:10, Paper FrB1.3

A Constraint Satisfaction Approach for Planning of Multi-Robot Systems (I)

<u>Panescu, Doru-Adrian</u> Gheorghe Asachi Tech. Univ. of Iasi

<u>Pascal, Carlos</u> Gheorghe Asachi Tech. Univ. of Iasi

r doodii, odiiioo

### 17:10-17:30, Paper FrB1.4

Spiking Neural Network for Controlling the Artificial Muscles of a Humanoid Robotic Arm (I)

Hulea, Mircea

Gheorghe Asachi Tech. Univ. of Iasi

Caruntu, Constantin - Florin

Gheorghe Asachi Tech. Univ. of Iasi

### 17:30-17:50, Paper FrB1.5

3D Complex Surface Generation through Procedural Robot Motion (I)

Borangiu, Theodor

Ciocan, Mihai

Pol. Univ. of Bucharest

### 17:50-18:10, Paper FrB1.6

Kinematic Evaluation of Articulated Rigid Objects (I)

Burlacu, Adrian

Gheorghe Asachi Tech. Univ. of Iasi

Condurache, Daniel

Gheorghe Asachi Tech. Univ. of Iasi

Clim, Eduard

Gheorghe Asachi Tech. Univ. of Iasi

# FrB2 Invited Session, Ara

#### Real Time Systems Applications

Chair: Popescu, Dumitru

Pol. Univ. of Bucharest

Co-Chair: Lupu, Ciprian

Pol. Univ. of Bucharest

Organizer: Popescu, Dumitru

Pol. Univ. of Bucharest

Organizer: Lupu, Ciprian

Pol. Univ. of Bucharest

# 16:10-16:30, Paper FrB2.1

Emergent Intelligence in Agents: A Scalable Architecture for Smart Cities (I)

Patrascu, Monica

Pol. Univ. of Bucharest

Dragoicea, Monica

Pol. Univ. of Bucharest

Ion, Andreea

Pol. Univ. of Bucharest

### 16:30-16:50, Paper FrB2.2

Real Time Agent Based Simulation for Smart City Emergency Protocols (I)

Dragoicea, Monica

Pol. Univ. of Bucharest

Patrascu, Monica

Pol. Univ. of Bucharest

Serea, George Alexandru

Pol. Univ. of Bucharest

#### 16:50-17:10, Paper FrB2.3

An Approach for Load Balancing in Virtual Power Plant Structures (I)

Lupu, Ciprian

Pol. Univ. of Bucharest

Oancea, Dumitru

Pol. Univ. of Bucharest

Oara, Cristian

Pol. Univ. of Bucharest

Lupu, Mircea

Transilvania Univ. of Brasov

Apetrei, Dan

ELSACO Energy

# 17:10-17:30, Paper FrB2.4

Real-Time Acquisition of Quality Verified Nonstandardized Color Images for Skin Lesions Risk Assessment – a Preliminary Study (I)

Udrea, AndreeaPol. Univ. of BucharestLupu, CiprianPol. Univ. of Bucharest

### 17:30-17:50, Paper FrB2.5

Designing Control Systems with Distributed Parameters (I)

Miron, Cristian

Pol. Univ. of Bucharest

Popescu, Dumitru

Pol. Univ. of Bucharest

Petrescu, Catalin

Pol. Univ. of Bucharest

### 17:50-18:10, Paper FrB2.6

Fuzzy Modeling and Control for a Road Section (I)

Dimon, Catalin

Pol. Univ. of Bucharest

Popescu, Dumitru

Pol. Univ. of Bucharest

Stefanoiu, Dan

Pol. Univ. of Bucharest

# FrB3 Regular Session, Carpati

### Applied Informatics

Chair: Postolache, Mihai Gheorghe Asachi Tech. Univ. of Iasi

Co-Chair: Ciobanu, Adrian Inst. of Computer Science, Romanian Acad. Iasi Branch

### 16:10-16:30, Paper FrB3.1

A Review of HDL-Based System for Real-Time Image Processing Used in Tumors Screening

<u>Chiuchisan, Iuliana</u>

Stefan Cel Mare Univ. of Suceava

<u>Geman, Oana</u>

Stefan Cel Mare Univ. of Suceava

### 16:30-16:50, Paper FrB3.2

A Study on Automatic Recognition of Positive and Negative Emotions in Speech

Pavaloi, Ioan

Inst. of Computer Science, Romanian Acad. Iasi Branch

Ciobanu, Adrian

Inst. of Computer Science, Romanian Acad. Iasi Branch

Luca, Mihaela

Inst. of Computer Science, Romanian Acad. Iasi Branch

Musca, Elena

Inst. of Computer Science, Romanian Acad. Iasi Branch

Barbu, Tudor

Inst. of Computer Science, Romanian Acad. Iasi Branch

### 16:50-17:10, Paper FrB3.3

Security Solution for Healthcare Hybrid Cloud Platform

Marcu, Roxana Elena Pol. Univ. of Bucharest

# 17:10-17:30, Paper FrB3.4

Uniformity and Correlation Test Parameters for Random Numbers Generators

Petrila, Iulian

Gheorghe Asachi Tech. Univ. of Iasi

Manta, Vasile

Gheorghe Asachi Tech. Univ. of Iasi

Ungureanu, Florina

Gheorghe Asachi Tech. Univ. of Iasi

### 17:30-17:50, Paper FrB3.5

Artificial Intelligence Application Built for ATS Detection with a New Portable Hollow Fiber IRAS

<u>Spectrometer</u>

Praisler, MirelaDunarea De Jos Univ. of GalatiCiochina, StefanutDunarea De Jos Univ. of GalatiStoica, AtanasiaDunarea De Jos Univ. of Galati

#### 17:50-18:10, Paper FrB3.6

CFD Simulation of the Airflow Pattern within a Three-Bed Hospital Room with or without a Portable Air Conditioner in Use

Vladut, Gabriel

S.C. IPA CIFATT Craiova

Sbirna, Liana Simona

Univ. of Craiova

Sbirna, Sebastian

St. Stephen Ec. School of Craiova

Codresi, Cristian

Sodinal Romania

Martin, Liviu

Turceni City Hospital

### FrB4 Regular Session, Laca

**Control Applications**

Chair: Valean, Honoriu Tech. Univ. of Cluj-Napoca

Co-Chair: Nitulescu, Mircea Univ. of Craiova

### 16:10-16:30, Paper FrB4.1

Dynamics Properties and Control for Oilwell Drillstrings

Bobasu, EugenUniv. of CraiovaIvanov, SergiuUniv. of CraiovaPopescu, DanUniv. of CraiovaRasvan, VladimirUniv. of Craiova

### 16:30-16:50, Paper FrB4.2

The Determination of the Maximum Energetic Zones for a Wind System, Operating at Variable Wind Speeds

Erdodi, Gheza-MihaiPol. Univ. of TimisoaraPetrescu, Doru-IonutPol. Univ. of TimisoaraSorandaru, CiprianPol. Univ. of TimisoaraMusuroi, SorinPol. Univ. of Timisoara

### 16:50-17:10, Paper FrB4.3

Modelling of Bio-Products Conversion Processes for Pollutant Compounds Formation Dynamics Assessment

Roman, Monica Univ. of Craiova

Selisteanu, Dan Univ. of Craiova

#### 17:10-17:30, Paper FrB4.4

Parameter Estimation Techniques for a Rehabilitation Hand Exoskeleton

Ivanescu, Mircea

Univ. of Craiova

Popescu, Dorin

Univ. of Craiova

Nitulescu, Mircea

Univ. of Craiova

Popescu, Nirvana

Pol. Univ. of Bucharest

### 17:30-17:50, Paper FrB4.5

Temperature Control of the Asphaltic Emulsion in an Industrial Tank

Muresan, VladTech. Univ. of Cluj-NapocaAbrudean, MihailTech. Univ. of Cluj-NapocaValean, HonoriuTech. Univ. of Cluj-NapocaColosi, TiberiuTech. Univ. of Cluj-Napoca

### 17:50-18:10, Paper FrB4.6

Variable DC Power Sources for 13C Isotope Separation Column Boiler Supply

Dulf, Eva HenriettaTech. Univ. of Cluj NapocaBoth, RoxanaTech. Univ. of Cluj-NapocaMunteanu, Radu A.Tech. Univ. of Cluj-NapocaFestila, ClementTech. Univ. of Cluj NapocaSecara, MihaiTech. Univ. of Cluj-Napoca

#### FrB5 Regular Session, Bucegi 1

**Nonlinear Systems**

Chair: Sima, Vasile National Inst. for Res. and Development in Informatics, Bucharest Co-Chair: Halas, Miroslav Slovak Univ. of Tech.

# 16:10-16:30, Paper FrB5.1

Modelling and Performance Analysis of an Urban Wastewater Treatment Plant

Luca, Laurentiu

Dunarea De Jos Univ. of Galati

Barbu, Marian

Dunarea De Jos Univ. of Galati

Caraman, Sergiu

Dunarea De Jos Univ. of Galati

### 16:30-16:50, Paper FrB5.2

Eigenvalues for a Nonlinear Time-Delay System

Halas, Miroslav Slovak Univ. of Tech. in Bratislava

### 16:50-17:10, Paper FrB5.3

Control-Oriented Modeling and Flight Dynamics Analysis of a Flexible Generic Hypersonic Vehicle

Zhu, JiaoBeihang UnivChen, WanchunBeihang UnivMa, HongzhongBeijing Electro-Mechanical Engineering InstYang, ZhihongBeijing Aerospace Tech. Inst

# 17:10-17:30, Paper FrB5.4

Imperialist Competitive Algorithm with Variable Parameters for the Optimization of a Fuzzy

Controller

<u>Ciurea, Stelian</u>

<u>Trifa, Viorel</u>

Lucian Blaga Univ. of Sibiu

Tech. Univ. of Cluj-Napoca

### 17:30-17:50, Paper FrB5.5

Nonlinear Fuzzy Control of Human Heart Rate During Aerobic Endurance Training with Respect to Significant Model Variations

Patrascu, Adrian

Babes-Bolyai Univ. of Cluj-Napoca

Patrascu, Monica

Pol. Univ. of Bucharest

Hantiu, Iacob

Babes-Bolyai Univ. of Cluj-Napoca

# 17:50-18:10, Paper FrB5.6

<u>Sampled-Data Robust Feedback Linearization Using Neural Network-Aided Unscented Kalman Filter</u>

Zaheer, AsimNational Univ. of Sciences and Tech. of IslamabadHasan, MomenaNational Univ. of Sciences and Tech. of IslamabadAli, UsmanNational Univ. of Sciences and Tech. of IslamabadSalman, MuhammadNational Univ. of Sciences and Tech. of Islamabad

# IEEE COPYRIGHT AND CONSENT FORM

To ensure uniformity of treatment among all contributors, other forms may not be substituted for this form, nor may any wording of the form be changed. This form is intended for original material submitted to the IEEE and must accompany any such material in order to be published by the IEEE. Please read the form carefully and keep a copy for your files.

| TITLE OF PAPER/ARTICLE/REPORT, INCLUDING ALL CON<br>Dual Priority Scheduling algorithm used in the nMPRA Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TENT IN ANY FORM, FORMAT, OR MEDIA (hereinafter, "the Work"):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMPLETE LIST OF AUTHORS: Lucian ANDRIES, Vasile Gheor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ghiță GĂITAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IEEE PUBLICATION TITLE (Journal, Magazine, Conference, E<br>Computing (ICSTCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Book): 2014 18th International Conference on System Theory, Control and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| COPYRI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IGHT TRANSFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | cs Engineers, Incorporated (the "IEEE") all rights under copyright that may exist in and to:<br>nitted to the IEEE by the undersigned based on the Work; and (b) any associated written or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CONSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VT AND RELEASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| consideration for his/her participation in the conference, hereby grants the IEEI record, digitize, broadcast, reproduce and archive, in any format or medium, conference; (b) any written materials or multimedia files used in connection "Presentation"). The permission granted includes the transcription and reprod recorded broadcast of the Presentation during or after the conference.  3. In connection with the permission granted in Section 2, the undersigned h likeness, voice and biographical information as part of the advertisement, district any claim based on right of privacy or publicity. | at a conference hosted or sponsored in whole or in part by the IEEE, the undersigned, in<br>E the unlimited, worldwide, irrevocable permission to use, distribute, publish, license, exhibit,<br>whether now known or hereafter developed: (a) his/her presentation and comments at the<br>m with his/her presentation; and (c) any recorded interviews of him/her (collectively, the<br>fuction of the Presentation for inclusion in products sold or distributed by IEEE and live or<br>sereby grants IEEE the unlimited, worldwide, irrevocable right to use his/her name, picture,<br>ribution and sale of products incorporating the Work or Presentation, and releases IEEE from |

| the Materials incorporate text passages, figures, data or other material from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ely, the "Materials") are original and that he/she is the author of the Materials. To the extent<br>e works of others, the undersigned has obtained any necessary permissions. Where necessary,<br>ant the license above and has provided copies of such permissions and consents to IEEE.                                                                                                                                                                                                                                                                                                                                                                                             |

| Please check this box if you do not wish to have video/audio recordings made reverse side for Retained Rights/Terms and Conditions, and Author Response                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NERAL TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The undersigned represents that he/she has the power and authority to make The undersigned agrees to indemnify and hold harmless the IEEE from any above.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | and execute this assignment.  damage or expense that may arise in the event of a breach of any of the warranties set forth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>In the event the above work is not accepted and published by the IEEE or is shall become null and void and all materials embodying the Work submitted</li> <li>For jointly authored Works, all joint authors should sign, or one of the author</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (I) Lucian ANDRIEŞ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.10.2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Author/Authorized Agent for Joint Authors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| U.S. GOVERNMENT EMPLOYED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E CERTIFICATION (WHERE APPLICABLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nd prepared the Work on a subject within the scope of their official duties. As such, the Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | above to enable the IEEE to claim and protect its copyright in international jurisdictions.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CROWN COPVEIGHT CEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RTIFICATION (WHERE APPLICABLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |